ماسفت قدرت

ماسفت قدرت (به انگلیسی: power MOSFET) یا VMOSFET، نوعی خاصی از ترانزیستور ماسفت است که به منظور کارکرد در توانهای بالا طراحی شدهاست.

در مقایسه با دیگر ادوات الکترونیک قدرت مانند (IGBT) یا تریستور، مهمترین مزایای ماسفت قدرت، سرعت سوئیچینگ بالا و کارایی خوب در ولتاژهای پایین است. همانند IGBT، در ماسفت قدرت هم از گیت عایق شدهاستفاده شدهاست که این امر عمل راه اندازی ترانزیستور را آسان میکند. این ماسفت در بهره کم نیز بکار میرود تا جایی که بعضاً لازم است ولتاژ گیت ترانزیستور بیشتر از ولتاژ تحت کنترل باشد.

طراحی ماسفت قدرت با توسعه تکنولوژی CMOS که برای ساخت مدارهای مجتمع در اواخر دهه ۱۹۷۰ صورت گرفت، آغاز شد. نحوه عملکرد ماسفت قدرت شبیه ماسفت معمولی است.

ماسفت قدرت، پرکاربردترین کلید مورد استفاده در ولتاژهای پایین (کمتر از 200 V) است که معمولاً در مدارات منابع تغذیه، مبدلهای DC به ac و کنترلکنندههای موتور بکار میرود.

ساختار پایه[ویرایش]

در اوایل دهه ۱۹۸۰ و همزمان با معرفی اولین ماسفت قدرت، ساختارهای متعددی ارائه شدند اما اغلب آنها (حداقل تا همین اواخر) کنار گذاشته شده و فقط ساختار ماسفت با نفوذ عمودی (VDMOS) مورد توجه قرار گرفت.[۱]

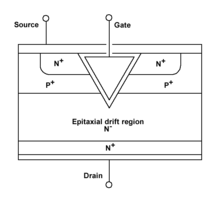

در شکل ۱، سطح مقطع یک VDMOS نشان داده شدهاست: دیده میشود که پایه سورس بالاتر از پایه درین قرار دارد که باعث میشود جریان الکتریکی به صورت "عمودی" جاری شود. واژه "نفوذ (دیفوژن)" که در اسم این نوع ترانزیستور وجود دارد، به پروسه ساخت آن مربوط میشود. نواحی +P و +N (شکل۱)، با استفاده از تکنیک دیفوژن ایجاد میشوند.

ماسفتهای قدرت ساختاری متفاوت از ماسفتهای معمولی دارند. بر خلاف اغلب ادوات الکترونیک قدرت که ساختاری مسطح (افقی) دارند، این المان دارای ساختار عمودی است. در یک ساختار مسطح، مقدار جریان و ولتاژ شکست هر دو تابعی از ابعاد کانال (به ترتیب عرض و طول کانال) هستند که در نتیجه سبب استفاده ناکارآمد از «سیلیکون و مستغلات» میشود. در ساختار عمودی، ولتاژ نامی ترانزیستور تابعی از دوپینگ و ضخامت لایه N است در حالی که مقدار جریان تابعی از عرض کانال است. این حالت سبب آن میشود که ترانزیستور بتواند ولتاژ و جریان بالا را در یک قطعه سیلیکون فشرده تحمل کند.

شایان ذکر است که ماسفت قدرت با ساختار افقی (عرضی) نیز وجود دارد که عمدتاً در تقویت کنندههای صوتی استفاده میشوند. مزیت آنها این است که رفتار بهتری در ناحیه اشباع به نسبت ترانزیستور با ساختار عمودی از خود نشان میدهند. ماسفتهای قدرت عمودی، برای کاربردهای کلیدزنی طراحی شدهاند و بنابراین فقط در حالت روشن یا خاموش بکار برده میشوند.

مقاومت در حالت روشن[ویرایش]

زمانی که ماسفت قدرت در حالت روشن قرار دارد، مقاومتی را مابین پایههای درین و سورس از خود نشان میدهد. همانطورکه در شکل ۲ دیده میشود، این مقاومت که RDSon نامیده میشود، مجموعی از چندید مقاومت اولیه است.

- RS مقاومت سورس است که نشان دهنده همه مقاومت بین الکترود سورس و کانال ماسفت است: مقاومت بین پایه سورس ماسفت و قسمت +N

- Rch مقاومت کانال است. این مقاومت، نسبت معکوس با عرض کانال و همچنین در یک ویفر سیلیکون، با چگالی کانال دارد. مقاومت کانال، یکی از عوامل مهم در تعیین مقاومت حالت روشن ماسفتهای ولتاژ پایین است و تلاشهای فراوانی در جهت کوچکتر کردن ابعاد کانال به منظور افزایش چگالی آن، در حال انجام است.

- Ra که به مقاومت دسترسی معروف است، نشان دهنده مقاومت ناحیه لایه نشانی شده در زیر ترمینال گیت است؛ محلی که حرکت جریان الکتریکی از شکل افقی (درون کانال)، به شکل عمودی (به سمت ترمینال درین) تغییر جهت پیدا میکند.

- Rn مقاومت قسمت لایه نشانی شدهاست. از آنجایی که نقش این لایه تحمل افت ولتاژ در حالت قطع ماسفت است، لذا مقدار این مقاومت بهطور مستقیم با ولتاژ نامی ماسفت در ارتباط است. یک ماسفت ولتاژ بالا نیازمند یک لایه ضخیم با ناخالصی پایین (مقاومت زیاد) در حالی که ماسفتی با ولتاژ پایین نیازمند یک لایه نازک با ناخالصی بالا (مقاومت کم) است؛ بنابراین در یک ماسفت ولتاژ بالا، Rn عامل اصلی در مقاومت کل ماسفت است.

- RD معادل مقاومت RS برای درین است. این مقاومت، نشان دهنده مقاومت بستر ترانزیستور است.

تعادل بین ولتاژ شکست و مقاومت حالت روشن[ویرایش]

هنگامی که ماسفت قدرت در حالت خاموش قرار دارد، معادل یک پیندیود است. زمانی که این ساختار بسیار نامتقارن تحت بایاس معکوس قرار میگیرد، ناحیه تخلیه، بیشتر به درون قسمتی که ناخالصی کمتری دارد، نفوذ میکند (ناحیه -N) و این بدان معناست که این لایه باید بتواند ولتاژ درین-سورس ماسفت را در حالت خاموش تحمل کند.[۲]

علاوه بر این، به علت اینکه لایه -N دارای ناخالصی کمی است، مقاومت این لایه، بالا بوده و سبب بالا رفتن مقاومت درین-سورس در حالت روشن میشود.

دو پارامتر اصلی تعیینکننده ولتاژ شکست و RDSon ترانزیستور عبارتند از: میزان ناخالصی و عرض لایه -N. هر چقدر این لایه عریضتر بوده و ناخالصی آن کمتر باشد، ولتاژ شکست ماسفت بیشتر میشود. در مقابل هر اندازه که این لایه کم عرض تر و با ناخالصی بالا باشد، مقاومت حالت روشن ماسفت RDSon (و در نتیجه تلفات هدایتی ماسفت)، کمتر میشود؛ بنابراین ملاحظه میشود که در طراحی ماسفت قدرت باید یک حالت تعادل یا میانه مابین مقاومت حالت روشن و ولتاژ شکست ماسفت برقرار شود.

دیود بدنه[ویرایش]

همانطورکه در شکل رو به رو دیده میشود، الکترود سورس به هر دو لایه +N و +P متصل است اما میدانیم که در ماسفت معمولی، پایه سورس تنها به لایه +N متصل میشود. حال اگر در ماسفت قدرت نیز بدین صورت عمل میشد، سبب معلق ماندن لایه +P مابین دو منطقه N (درین و سورس) میشود که معادل یک ترانزیستور NPN که پایه بیس آن به جایی متصل نیست، میشود. این ترانزیستور پارازیتی، سبب بهم خوردن عملکرد ماسفت در شرایط خاص میشود. اتصال الکترود سورس به هر دو لایه +P و +N سبب میشود که پایه بیس این ترانزیستور به پایه امیتر آن وصل شده و همانند یک دیود عمل کند.

دیود بدنه ممکن است به عنوان دیود هرزگرد در بارهای سلفی که در پل اچ یا نیم پل وجود دارد، استفاده شود. با وجود اینکه این دیود افت ولتاژ بالایی در بایاس مستقیم دارد، میتواند جریانهای بالا را تحمل کند و در اکثر کاربردها کافی بوده و نیاز به استفاده از دیود مستقل دیگری در بیرون بستهبندی ماسفت قدرت نیست.

به دلیل تک قطبی بودن ماسفت قدرت، میتواند در سرعتهای بسیار بالا عمل کلیدزنی را انجام دهد و نیازی به تخلیه شدن حاملهای اقلیت همانند آنچه که در ادوات دو قطبی اتفاق میافتد، نیست.

عملیات کلیدزنی[ویرایش]

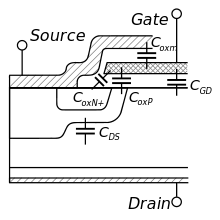

تنها محدودیت ذاتی در کاهش سرعت کلیدزنی، خازنهایی داخلی ماسفت است. (شکل ۴ را ببینید). این خازنها باید در هنگام سوئیچ کردن ترانزیستور، شارژ و تخلیه شوند. این فرایند میتواند کند باشد زیرا جریانی که از طریق خازن گیت جاری میشود، توسط مدار خارجی محدود میگردد. در واقع این مدار خارجی سرعت کلیدزنی ترانزیستور را تعیین میکند.

خازنها[ویرایش]

در دیتاشیت ماسفت، خازنهای مختلفی با نامهای Ciss (خازن ورودی در حالتی که پایههای درین و سورس به هم متصل هستند), Coss (خازن خروجی در حالتی که گیت و سورس به هم متصل هستند) و Crss (خازن انتقال معکوس در حالتی که پایه سورس به زمین متصل است) به چشم میخورد.

خازن گیت-سورس[ویرایش]

خازن CGS تشکیل شدهاست از اتصال موازی CoxN+CoxP و Coxm (شکل ۴ را ببینید). به دلیل اینکه نواحی +N و +P دارای ناخالصی بالایی هستند، لذا خازنهای سری با هم، ثابت هستند. Coxm خازن مابین عایق گیت و الکترود سورس بوده و بنابراین مقدار آن نیز ثابت است. از این رو، ثابت فرض کردن CGS، تقریب صحیحی است بدین معنا که مقدار این خازن وابسته به نقطه کار ماسفت نیست.

خازن گیت-درین[ویرایش]

خازن CGD را میتواند همانند اتصال سری دو خازن اولیه دانست. اولی عبارت است از خازن اکسید (CoxD) که تشکیل شدهاست از الکترود گیت، عایق دیاکسید سیلیکون و قسمت بالای لایه +N و مقدار آن ثابت است. دومی خازن (CGDj) است که ناشی از گسترش ناحیه تخلیه در زمانی که ماسفت خاموش میباشد، است که در نتیجه مقدار این خازن تابعی از ولتاژ درین-سورس است. CGDj (و در نتیجه CGD) خازنی است که مقدار آن وابسته به ولتاژ گیت-درین است. اگر این ولتاژ افزایش یابد، مقدار ظرفیت خازن کم میشود. زمانی که ماسفت در حالت روشن است، CGDj به حالت موازی درآمده و بنابراین خازن گیت به درین برابر با CoxD که یک مقدار ثابت است، میشود.

خازن درین-سورس[ویرایش]

در وضعیتی که الکترود سورس، لایه +P را نیز میپوشاند (نگاه کنید به شکل ۱)، پایههای درین و سورس توسط یک پیوند P-N از همدیگر جدا میشود؛ بنابراین CDS، خازن پیوند است.

دیگر عوامل دینامیکی[ویرایش]

اندوکتانس بستهبندی[ویرایش]

به منظور کارکرد یک ماسفت، باید به مدار خارجی وصل شود که اغلب اوقات از اتصال سیمی (اگر چه تکنیکهای جایگزین کشف شدهاست) استفاده میشود. اتصالات سیمی (پایههای ماسفت)، از خود خاصیت سلفی ناخواستهای نشان میدهند که تأثیر منفی بر سرعت کلیدزنی ماسفت میگذارد. این اندوکتانس ناخواسته، تمایل دارد که جریان خود را ثابت نگه دارد، همچنین باعث ایجاد اضافه ولتاژ معکوس در زمان خاموش شدن ماسفت شده و تلفات کلیدزنی را افزایش میدهد.

برای هر یک از پایههای ماسفت میتوان یک سلف پارازیتی در نظر گرفت که اثرات مختلفی را دارند که عبارتند از:

- اندوکتانس ناخواسته پایه گیت تأثیر کمی دارد (با فرض اینکه مقدار آن کمتر از چند صد نانو هانری است). در برخی موارد، اندوکتانس گیت و خازن ورودی ترانزیستور میتواند یک نوسانساز تشکیل دهد. باید از این حالت اجتناب شود چراکه سبب افزایش شدید تلفات کلیدزنی میشود (منجر به تخریب قطعه). در طراحیها، اندوکتانس ناخواسته پایین نگه داشته میشود تا از این پدیده جلوگیری شود.

- اندوکتانس درین، در هنگام روشن شدن ماسفت تمایل به کاهش ولتاژ درین را دارد که سبب کاهش تلفات روشن شدن ماسفت میشود. با این حال به دلیل اینکه این اندوکتانس سبب تولید اضافه ولتاژ در موقع قطع ماسفت میشود، تلفات خاموش شدن را افزایش میدهد.

- اندوکتانس سورس، اثری مشایه با اندوکتانس درین دارد. علاوه بر آن، به دلیل به وجود آمدن یک اثر فیدبک، سبب طولانیتر شدن کموتاسیون و در نتیجه افزایش تلفات میگردد.

مقادیر حد[ویرایش]

شکست عایق گیت[ویرایش]

عایق گیت بسیار نازک است (100 نانومتر یا کمتر)، بنابراین قادر به تحمل ولتاژ محدودی میباشد. در دیتاشیت محصول، به مقدار ماکزیمم ولتاژ گیت-سورس اشاره میشود (در حدود ۲۰ ولت). هر گونه افزایش ولتاژ از این مقدار سبب آسیب دیدن قطعه میشود. علاوه بر این، افزایش ولتاژ گیت-سورس، طول عمر ماسفت را بهطور چشمگیری کاهش میدهد در حالی که تأثیر چندانی بر کاهش RDSon ندارد.

برای مقابله با این مسئله، اغلب از مدار راه انداز گیت استفاده میشود.

حداکثر ولتاژ درین-سورس[ویرایش]

ماسفت قدرت یک مقدار ماکزیمم مشخصی برای ولتاژ درین-سورس دارد (در حالت خاموش) که مقداری فراتر از آن ممکن است سبب شکست شود. افزایش ولتاژ به مقدار بیش از ولتاژ شکست، به صورت بالقوه سبب آسیب رساندن به خود قطعه و دیگر عناصر مدار به دلیل اتلاف بیش از حد انرژی میشود.

حداکثر جریان درین[ویرایش]

جریان درین در حالت کلی باید از یک مقدار مشخصی کمتر باشد (حداکثر جریان پیوسته درین). مقدار این جریان میتواند به مقادیر بالاتری برای مدت زمان بسیار کوتاه (حداکثر جریان درین به صورت پالس) برسد. جریان درین توسط تلفات اهمی محدود میشود.

حداکثر درجه حرارت[ویرایش]

درجه حرارت پیوند (TJ) ماسفت باید کمتر از یک مقدار مشخص باشد تا قطعه بتواند به درستی کار کند. معمولاً بستهبندی قطعه، حداکثر دمای مجاز پیوند را محدود میکند.

حداکثر دمای محیط برای کارکرد صحیح ماسفت، بر اساس تلفات توان و مقاومت حرارتی تعیین میشود. این مقاومت حرارتی شامل مقاومت حرارتی بین پیوند و بدنه قطعه و همچنین مقاومت حرارتی بین بدنه قطعه و هوای اطراف است. برای کاهش این مقاومت حرارتی از هیت سینک استفاده میشود.

انواع ساختارهای ماسفت قدرت[ویرایش]

VMOS[ویرایش]

در VMOS از یک ساختار شیاری به شکل V استفاده شدهاست و برای اولین بار در المانهای تجاری بکار رفت.[۳]

UMOS[ویرایش]

در این MOSFET قدرت، الکترود گیت در شیاری که در داخل سیلیسیوم ایجاد شدهاست، دفن میشود که موجب پدید آمدن کانالی به صورت عمودی میشود. علت اصلی نامگذاری این ماسفت، فرم U شکل شیار گیت است.

جستارهای وابسته[ویرایش]

منابع[ویرایش]

- ↑ Pierre Aloïsi, Les transistors MOS de puissance in Interrupteurs électroniques de puissance, traite EGEM, under the direction of Robert Perret, Lavoisier, Paris, 2003 [in French] ISBN 2-7462-0671-4

- ↑ Duncan A. Grant, John Gowar POWER MOSFETS: Theory and Applications John Wiley and Sons, Inc ISBN 0-471-82867-X , 1989

- ↑ Duncan A. Grant, John Gowar POWER MOSFETS: Theory and Applications John Wiley and Sons, Inc [[:en:Special:BookSources/047182867X| ISBN 0-471-82867-X]] , 1989